穿起小“马甲” 解读Cortex-A17

Cortex-A12的改进在哪里?

对于Cortex-A12在架构方面的改进,可以简单归纳如下:

Cortex-A12的指令集使用了更新的ARMv7-A,相比之前Cortex-A9的ARMv7,新版本的CPU内存寻址空间可以提升至1TB。其他技术方面,ARMv7-A可以支持单周期执行两条ARM指令,NENO SIMD指令集可以操作128bit寄存器,NENO可以高同时操作16个8bit数据、支持虚拟化技术、支持128bit的AXI4总线。

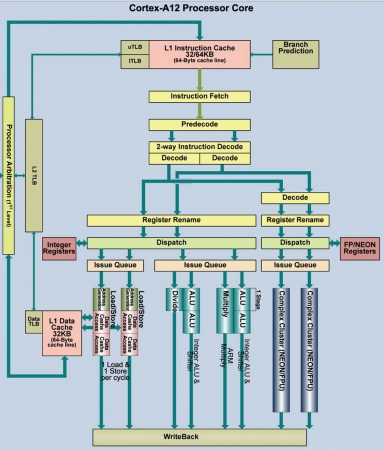

Cortex-A12流水线深度为10~12级,L2缓存彻底内置,所有核心共享L2缓存,整体架构更为先进。在浮点能力方面,Cortex-A12采用了第四版NENO单元和vFP单元,性能更强。架构方面,Cortex-A12前端采用了双Decoder单元,兼顾功耗和性能。在分支单元上,Cortex-A12的分支单元相比之前的Cortex-A9要强很多,分支预测能力更为优秀。在计算单元部分,Cortex-A12的三个指令排序单元分别跟着两个乱序整数ALU、两个乱序地址产生单元和两个乱序的FP/NENO单元—Cortex-A12还将Cortex-A9上原本为顺序的浮点和地址单元改成了乱序执行,配合更为强大的指令排序单元,进一步加强了CPU的性能和效率。

从整体架构改进的角度来看,Cortex-A12相比之前的Cortex-A9,在特定的频率和工艺下,性能提升大约有30%~40%。Cortex-A12和Cortex-A9在架构继承上的关系不明显,内核部分反倒更像Cortex-A15的缩减版本。

Cortex-A12架构图。双指令发射和尽量偏向性能功耗比的设计使得其定位被限制在主流市场。

联发科的MT6595

作为目前首款发布并有实物展示的Cortex-A17架构的产品,联发科MT6595可谓出尽了风头。这颗SoC采用了big.LITTLE技术,集成了四颗Cortex-A17核心和四个Cortex-A7核心,CPU高频率达到2.2GHz~2.5GHz。GPU方面使用了PowerVR G6200系列GPU,这颗GPU曾经被使用在苹果A7上,即使联发科使用的GPU规模有所缩水,但性能肯定也不容小觑。尤其值得一提的是,MT6595集成了全新基带,支持LTERelease9 Cat.4,并支持TD-LTE、FDD-LTE以及HSPA+、TDSCMDA、EDGE、GSM等几乎全通讯模式。